#### **APR, 2009**

# Technology progress of advanced gate stack and reliability issues

**Rino Choi**

Inha University

#### **Gate Stack Scaling**

#### **Objectives**

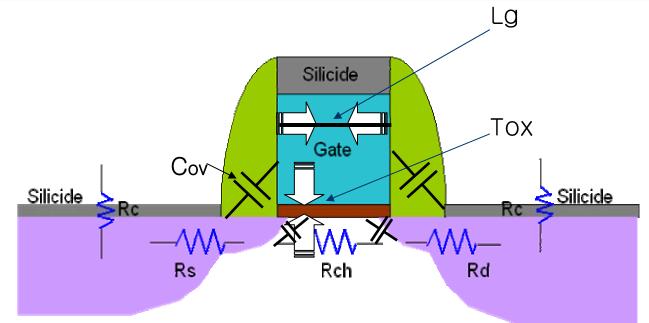

- Scale electrical (equivalent oxide) thickness of SiO<sub>2</sub> dielectric

- Maximize Ion at a tolerable Ioff

- Little or no mobility degradation

- No reliability impact (TDDB, QBD, NBTI, hot e)

- Scale Lg to maximize performance gain and minimize delay  $\tau$

- (worsens Short Channel Effects)

- Minimize depletion from (poly-Si0 electrode

- Adds to electrical thickness of gate dielectric

## High-k/metal gate solution I

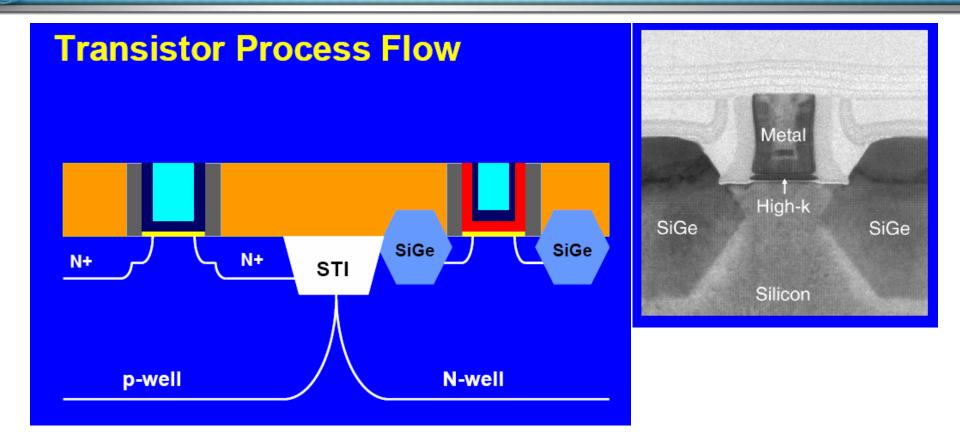

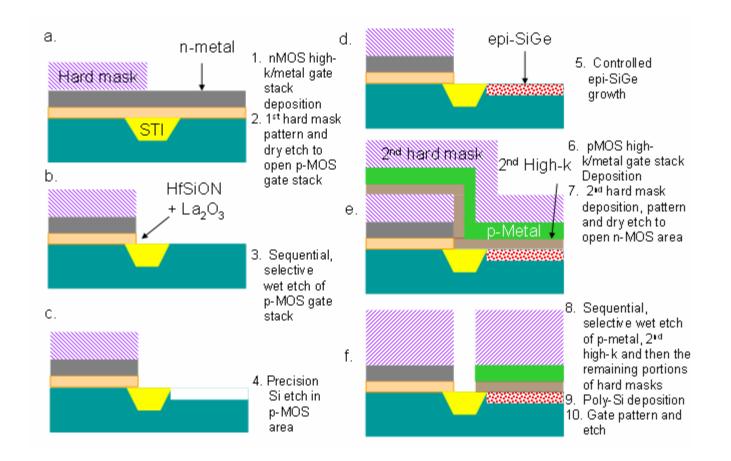

- In Feb, 2007, INTEL announced that it has implemented two materialshigh-k dielectrics and metal gates for the technology

- In IEDM 2007, Intel presented dual replacement gate process for metal gate with extremely improved pFET performance

### High-k/metal gate solution II

In 2007 VLSI, SEMATECH published a novel high-k integration scheme using SiGe for PMOSFET for Vt control

Δ

#### Overview of technology progress

- High-k Dielectric scaling

- Metal gate electrode

- Reliability methodologies and status

- Charge trapping and BTI

- Breakdown

5

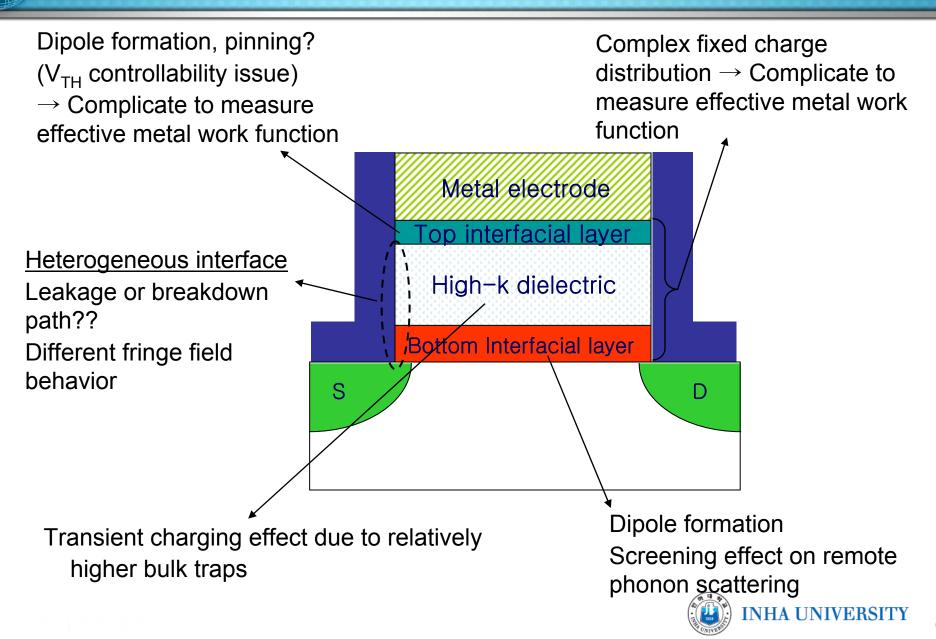

### New materials require new methodologies

#### **Demand on new methodologies**

- Metal gate/high-k gate stack devices have physical and electrical properties different from conventional polysilicon/ SiO<sub>2</sub> gate stack devices

- Dielectric stack consists of multiple layers

- Smaller bandgap and bandgap offsets

- Influence of metal electrodes

- Transient charging effects (TCE)

⇒ Hard to import and apply SiO<sub>2</sub> test methodologies ⇒ Needs novel methodologies to decouple contributions from different components of the gate

- Simple and low cost manufacturing than silicon CMOS chip

- Intrinsic potential to improve chip performance by orders of magnitude not only a diminutive or incremental difference

- Feasibility to achieve super-high integration density greater than 10<sup>10</sup> transistors or other computing components per circuit

- High reproducibility to manufacture

- High reliability at least comparable to silicon chips in terms of key component lifetime

- Remarkably lowered power dissipation

- Former colleagues in SEMATECH

- Prof. Hwang's group in GIST

- Prof. Neugroschel in UF

Q