## Nano-HEMTs Fabricated by utilizing Nebased Atomic Layer Etching

S.H. Shin<sup>1</sup>, T.W. Kim<sup>1</sup>, J.I. Song<sup>1</sup>, G.Y. Yeom<sup>2</sup>, and J.H. Jang<sup>1</sup>

Gwangju Institute of Science & Technology Department of Information & Communications Department of Materials Science and Engineering SKKU

### Outline

- Introduction

- 1. High speed electronic devices

- 2. Key fabrication processes for Nano-HEMTs

- 3. Two step recess technology employing atomic layer etching

- Atomic Layer Etching

- ✓ Properties of the etched surface (Selectivity, XPS, and AFM)

- ✓ Characteristics of Vertical Schottky Diodes

- DC and RF Characteristics of Nano-HEMTs

- ✓ Depletion-mode InAs Composite Channel p-HEMTs

- ✓ Enhancement-mode InAs Composite Channel p-HEMTs

- Conclusions

WAVE-OPTOELECTRONIC

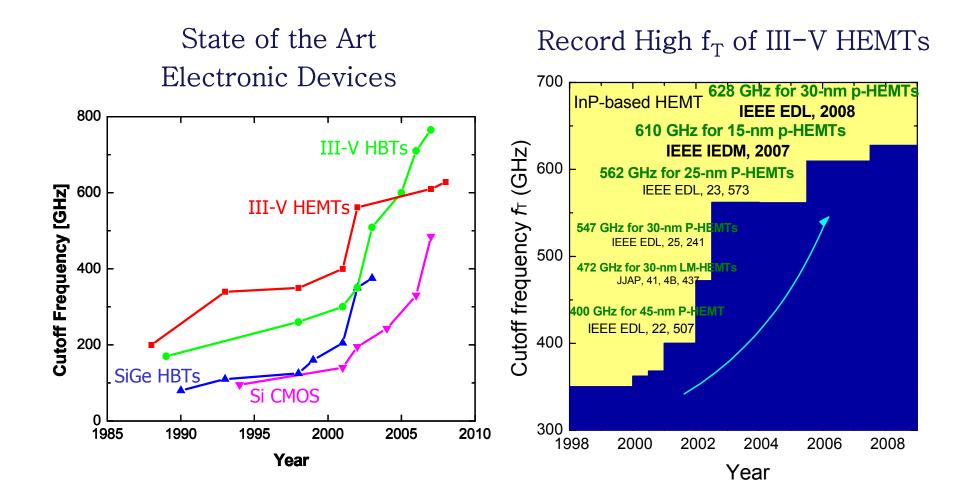

#### Overview of Ultra-fast Electronic Devices

#### < Ref. : Shinohara *et al.* (IPRM 2004) >

Gwangju Institute of Science and Technology Department of Information and Communications

3

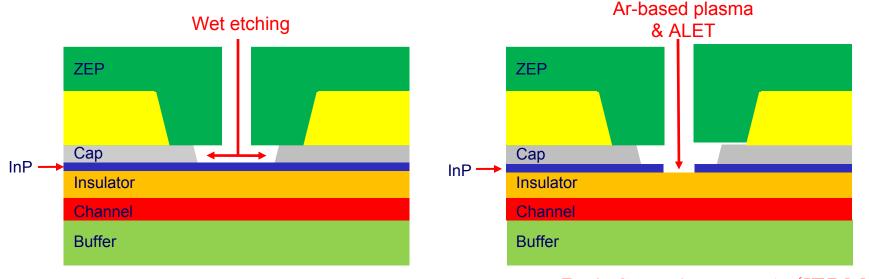

#### Gate Recess: Critical Process for Nano-HEMT

- Two-step recess for HEMT fabrication

- 1<sup>st</sup> step: wet etch  $\rightarrow$ n<sup>+</sup> InGaAs/InAlAs multi-layer cap removal

- $2^{nd}$  step: dry etch  $\rightarrow$  InP etch stop layer removal:

- Ar-based RIE (Conventional)

- or Ne-based atomic layer etching (ALET)

<Ref: Suemitsu et al. (IEDM 98)>

MICROWAVE-OPTOELECTRONIC

- Problems of Conventional Ar-based RIE

- Low etch selectivity

- Electrical & physical damage:  $\leftarrow$  Ion bombardment

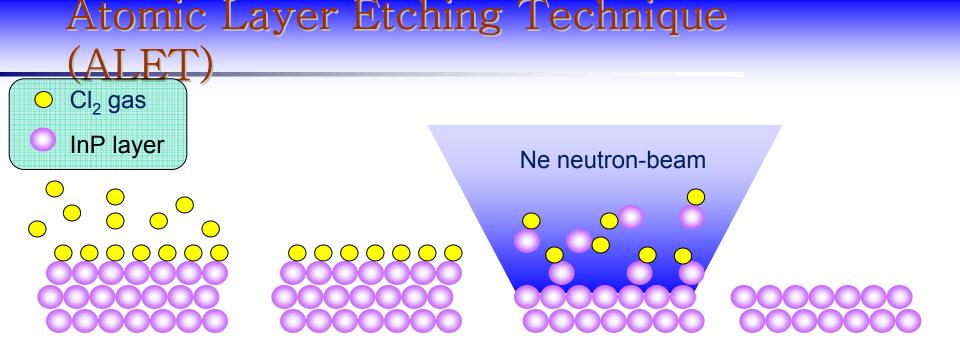

#### **Reactant Feed**

Reactantmoleculesadsorb onto a substratesurface.The etchantdoes not spontaneouslyetch the substrate.

#### Reactant Purge

Excess reactant is purged

#### Beam Irradiation

An energetic beam irradiates the surface, and surface atoms bonded with reactant are etched off owing to beaminduced chemical etching.

#### Product Purge

Etching products are purged after which one cycle of digital etching is completed

MICROWAVE-OPTOELECTRONIC

- The expected advantages of Ne-based ALET over Ar-based RIE

- The higher etch selectivity (ALET)

- The lower electrical & physical damage < Low energy neutral

#### beam

Gwangju Institute of Science and Technology Department of Information and Communications

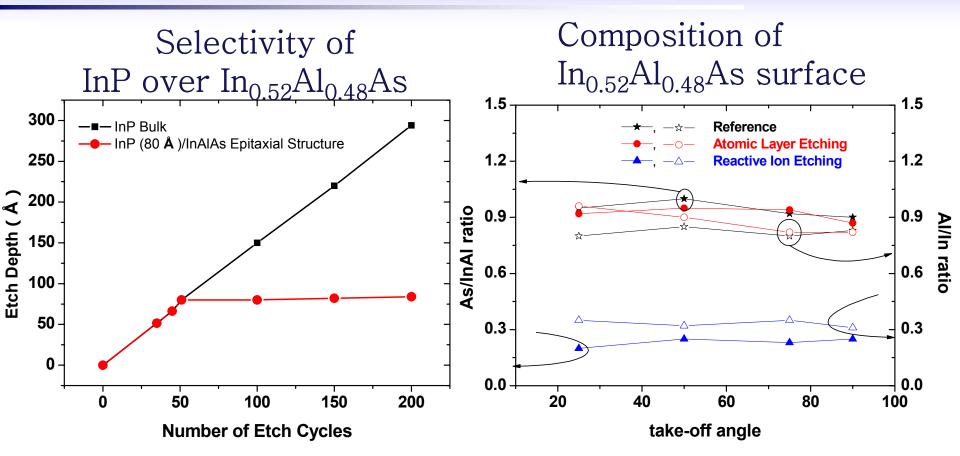

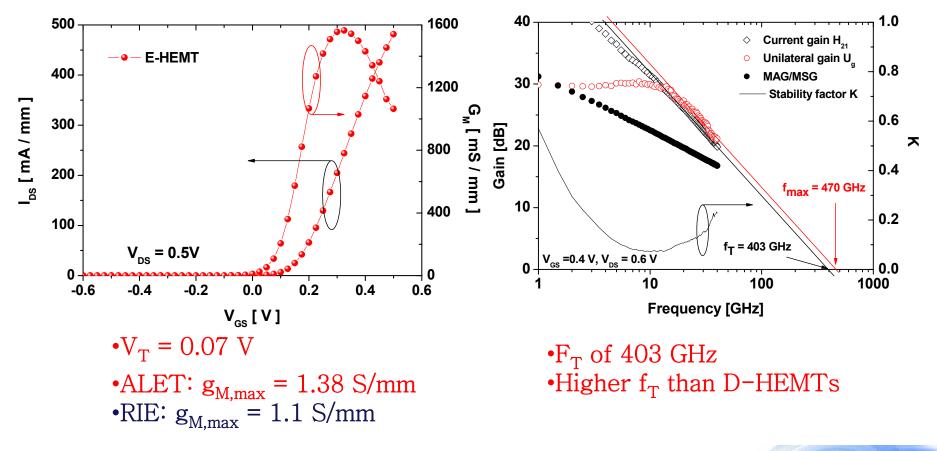

## **Etching Property of ALET**

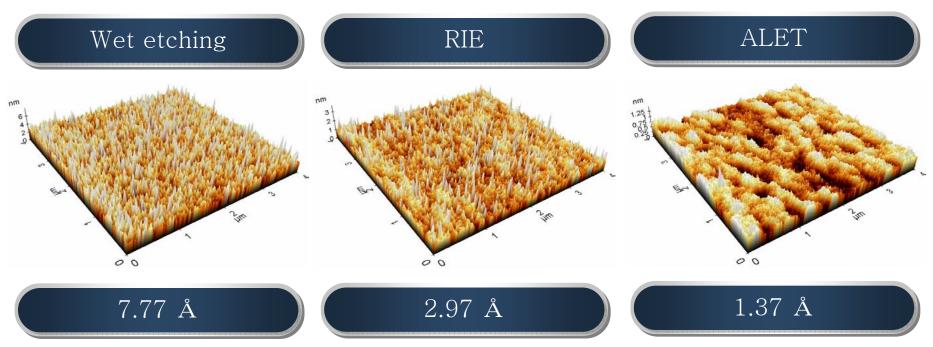

- Very high selectivity of InP over InAlAs (~70) cf) Ar-based RIE (~20)

- Minimal surface modification

### Surface Roughness

AFM image

The smallest rms roughness achieved by ALET process

Gwangju Institute of Science and Technology Department of Information and Communications

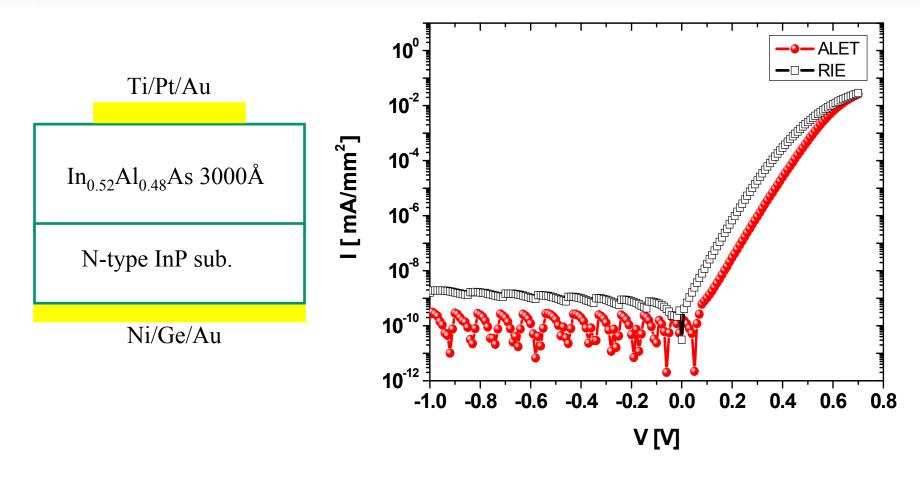

### Vertical Schottky Diode

RIE:

$$\Phi_{\rm B}$$

= 0.56 eV, η = 1.25

→ ALET:  $\Phi_{\rm B}$  = 0.64 eV, η = 1.17

#### The Fabricated Devices

MICROWAVE-OPTOELECTRONIC MIDAS

Gwangju Institute of Science and Technology Department of Information and Communications

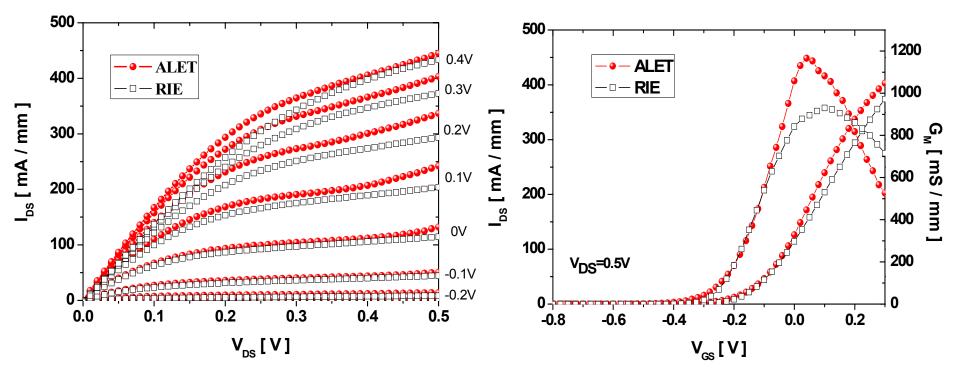

### 60-nm Depletion-Mode p-HEMTs

#### DC Characteristics

• $G_{M,Max}$  of the p-HEMTs fabricated by the ALET process was larger than that of the p-HEMT fabricated by the Ar-based RIE by 21%  $\rightarrow$  much lower plasma-induced damage characteristics of the ALET process

Gwangju Institute of Science and Technology Department of Information and Communications

OWAVE-OPTOELECTRONIC

### 60-nm Depletion-Mode HEMTs

**RF** Characteristics

Gwangju Institute of Science and Technology Department of Information and Communications

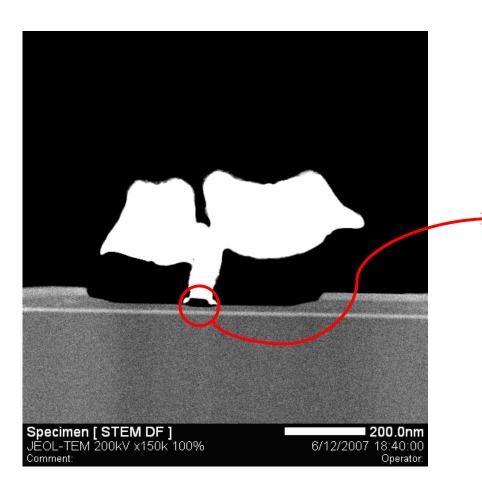

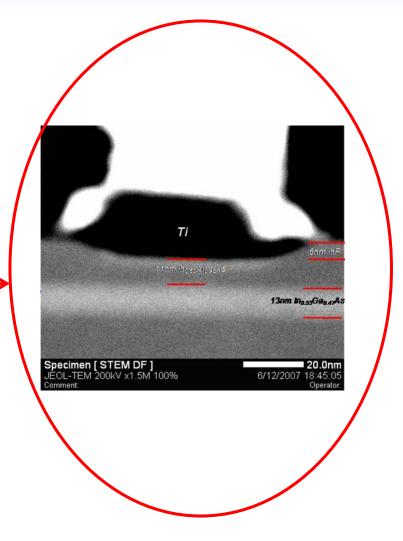

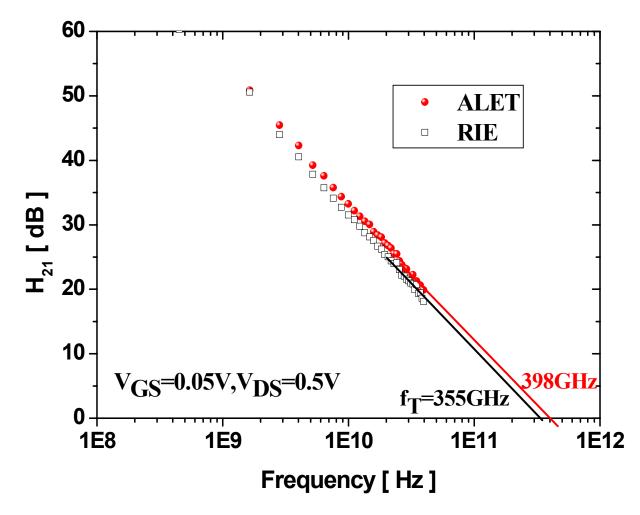

#### Enhancement-mode HEMT (E-HEMTs)

- E-HEMTs were fabricated by utilizing buried-Pt gate

- Gate metal stack: Pt(6 nm)/Ti/Pt/Au

- Post-annealing was carried out to drive Pt into InAlAs

Gwangju Institute of Science and Technology Department of Information and Communications

### Conclusions

•The effect of ALET in the two-step gate recess process

- Higher InP etch selectivity against the underlying In<sub>0.52</sub>Al<sub>0.48</sub>As barrier layer

- $\rightarrow$  Better uniformity of device characteristics

- ✓Less plasma-induced damage compared to conventional Arbased RIE process

- ✓ The smoother etched surface

- $\rightarrow$  Better gate diode characteristics

- The higher transconductance

- The lower subthreshold slope

Buried Pt gate

- The thinner effective Schottky layer thickness

- $\rightarrow$  Alleviation of short channel effect

- $\rightarrow$  Better gate modulation characteristics

- The higher Schottky barrier height due to the annealed Pt

- → Positive shift of threshold voltage

- $\rightarrow$  The smaller gate leakage current

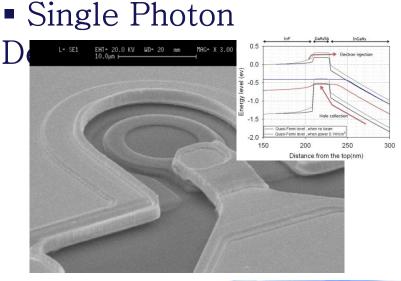

### Other Interesting Stuffs !!!

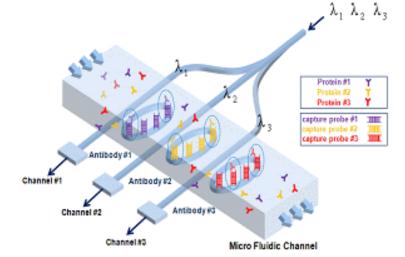

Ring resonator based Optical Filters and Biosensors

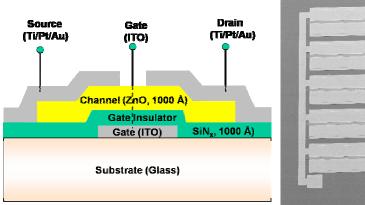

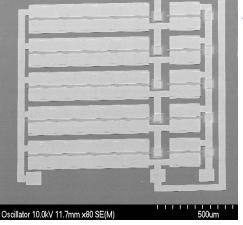

#### Oxide Thin Film Transistors

Gwangju Institute of Science and Technology Department of Information and Communications

14

# Thank You!!

Gwangju Institute of Science & Technology Department of Information & Communications