### DECADAL PLAN FOR SEMICONDUCTORS AND NANOTECHNOLOGY

Victor Zhirnov Chief Scientist Victor.Zhirnov@src.org Victor Zhirnov Semiconductor Research Corporation

The 17th U.S.-Korea Forum on Nanotechnology: Next-Generation Semiconductors and the Environmental Implications of Semiconductor Manufacturing

# Outline

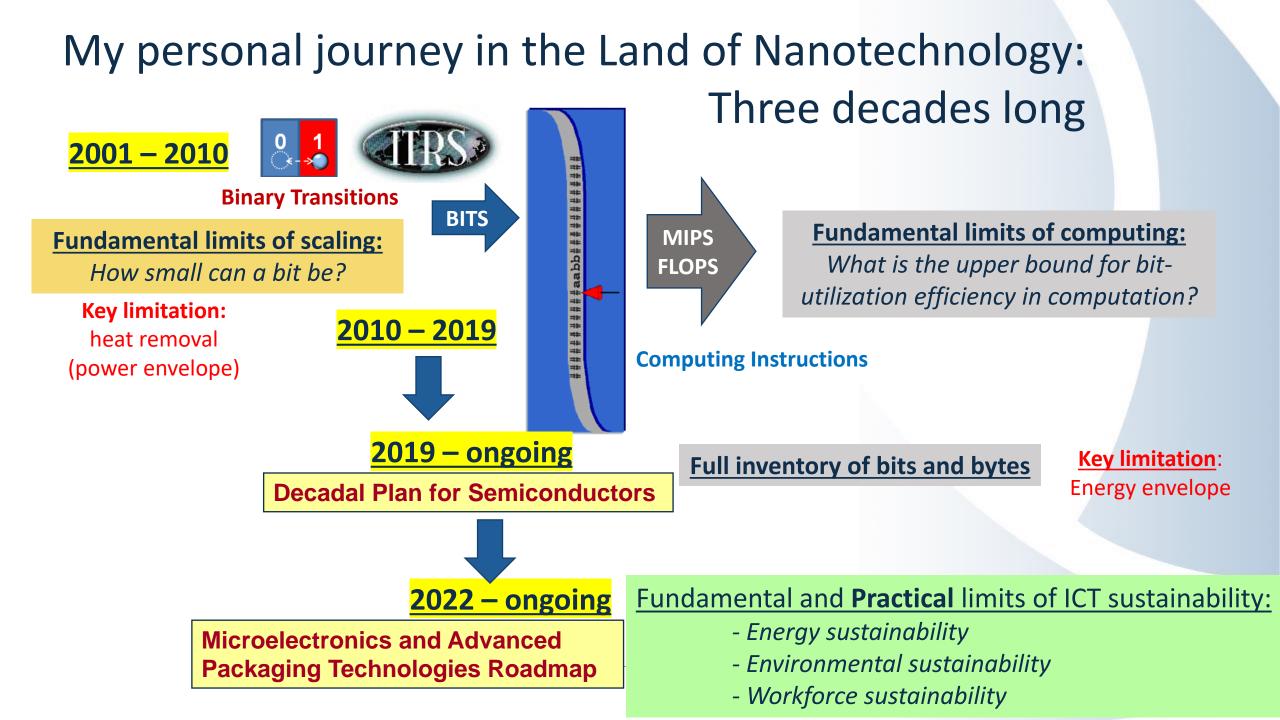

- My personal journey in the Land of Nanotechnology

- Decadal Plan for Semiconductors

- Global data storage inventory

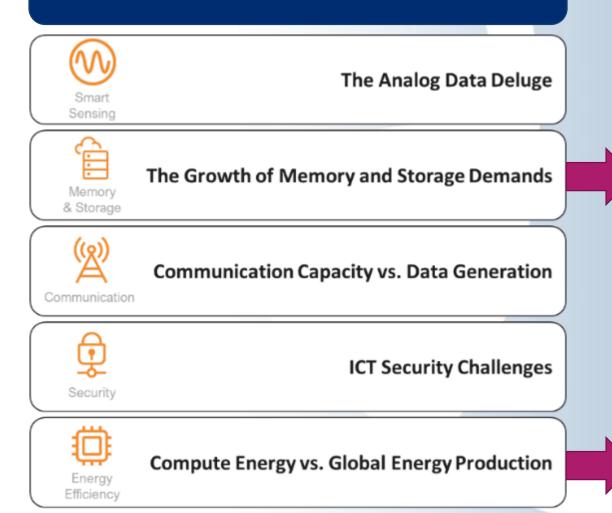

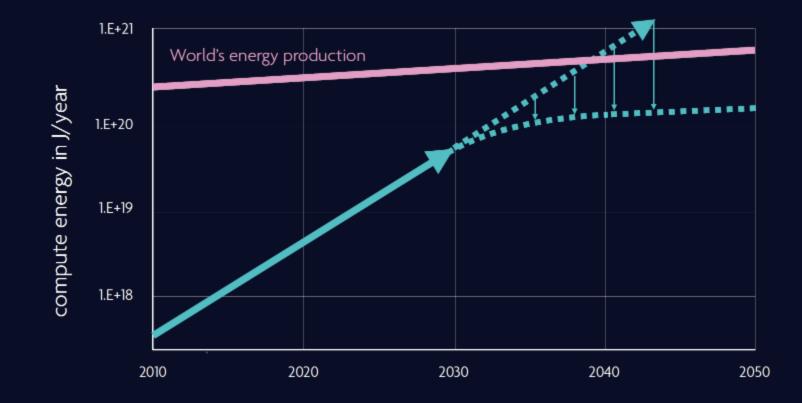

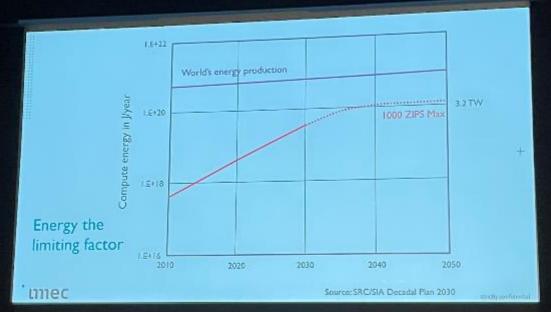

- Compute energy problem

- Microelectronics and Advanced Packaging Roadmap

- Energy sustainability

- Environmental sustainability

- Workforce sustainability

- Summary

### Limits to Binary Logic Switch Scaling—A Gedanken Model

VICTOR V. ZHIRNOV, RALPH K. CAVIN, III, FELLOW, IEEE, JAMES A. HUTCHBY, SENIOR MEMBER, IEEE, AND GEORGE I. BOURIANOFF, MEMBER, IEEE

Invited Paper

# **How Deep Can Multicore Processing Go?**

By <u>Mark LaPedus</u> <u>EE Times</u>

February 15, 2007 09:07 PM

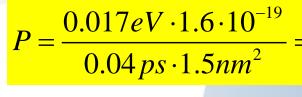

Mark Bohr, an Intel senior fellow and director of process <u>architecture</u> and integration at the microprocessor giant, said that future devices could theoretically scale down to 1.5-nm, with 0.04-ps switching speeds and 0.017 electron volts in terms of power consumption.

Bohr's forecast was based on a paper by V. Zhirnov in the November 2003 issue of "Proceedings of IEEE," where the minimum quantum well dimensions were estimated to be 1.5-nm.

$P = 3,000,000 \frac{W}{cm^2}$

Limits of Cooling?

6000 W/cm<sup>2</sup>

Sun

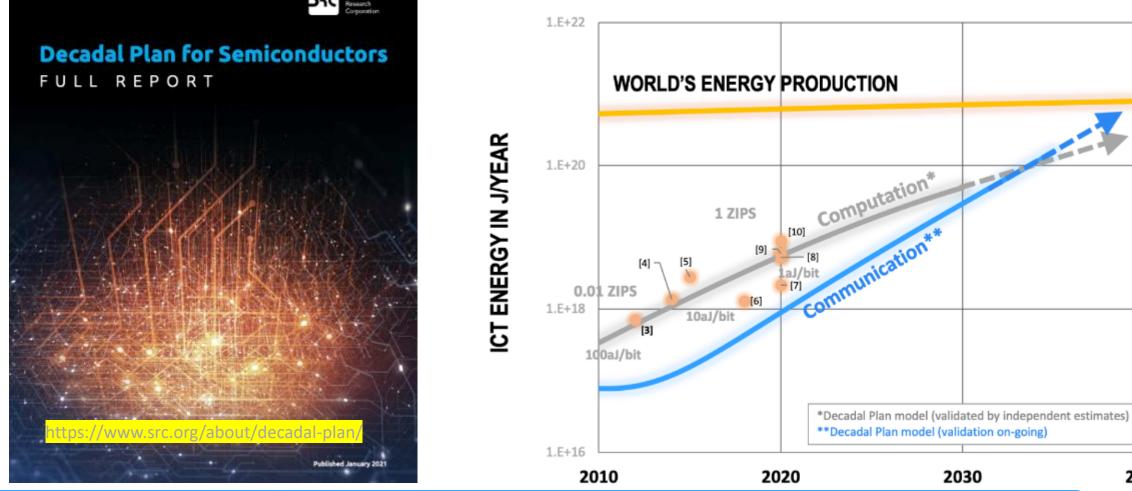

#### Decadal Plan for Semiconductors FULL REPORT

https://www.src.org/about/decadal-plan/

#### **Five "Seismic Shift" Research Priorities**

By design, the Decadal Plan focuses on WHAT to accomplish, not HOW to accomplish it.

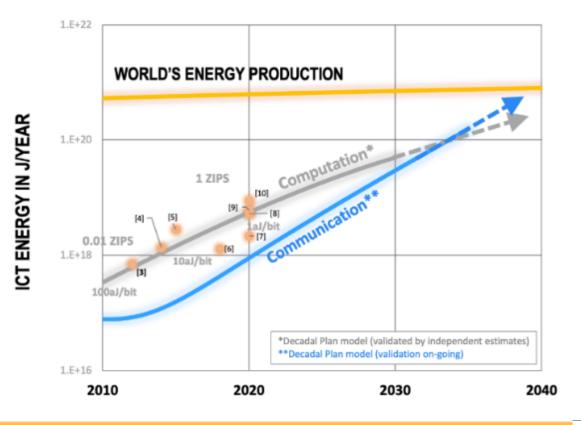

### ICT ENERGY COMPUTATION AND COMMUNICATION

By design, the Decadal Plan focuses on WHAT to accomplish, not HOW to accomplish it.

2040

# JRC

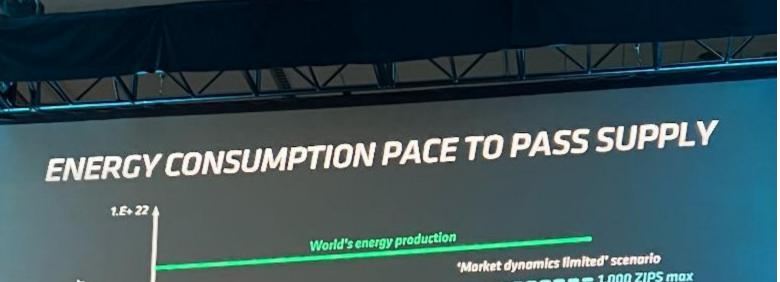

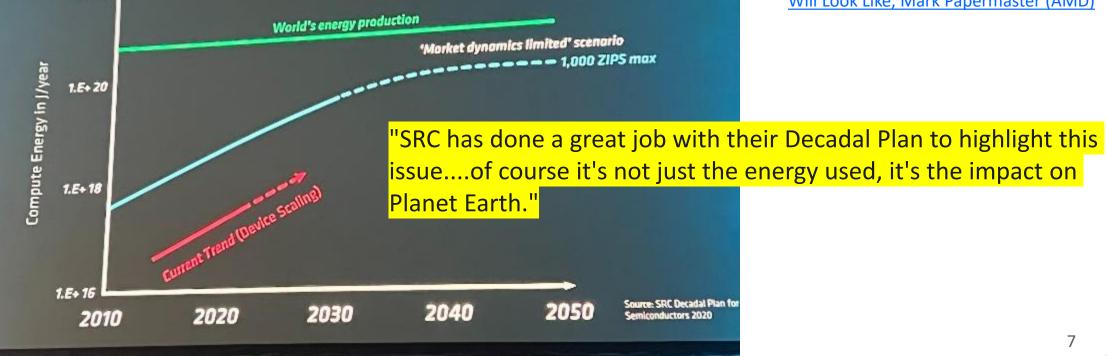

### Opening keynote talk at DAC 2022 (by Mark Papermaster, AMD CTO)

Semi Engineering - What Future Processors Will Look Like, Mark Papermaster (AMD)

#### The Endless Proceed of Moore's Law

unec

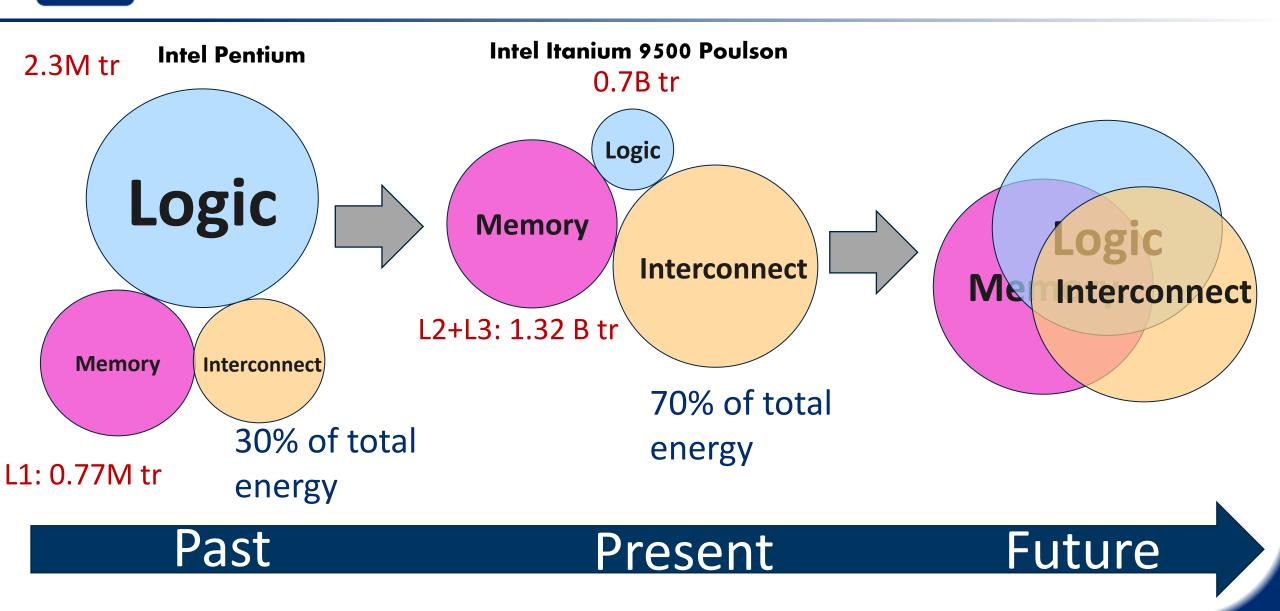

Luc Van den Hove's presentation slides 16-17

### + Luc Van den hove - President & CEO Inec New energy-efficient computational concepts become critical

Source: SRC decadal plan 2020

### A Future Shaped by Energy

imec

embracing a better life

Jan M. Rabaey

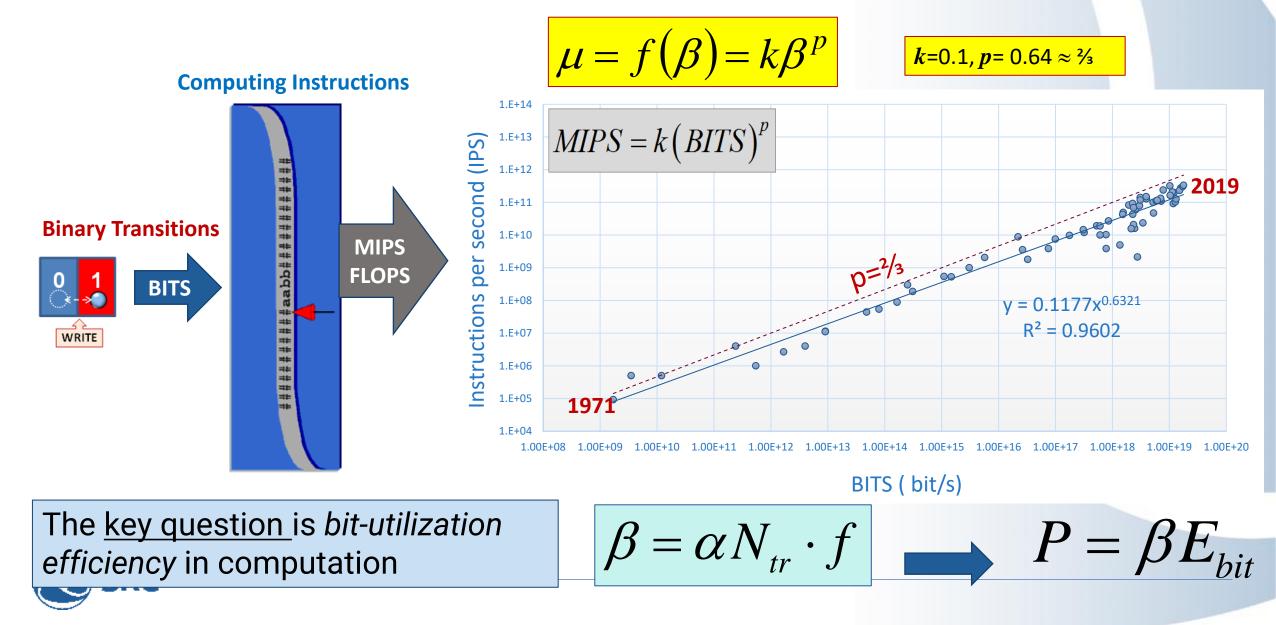

### **CPU operations vs. binary transitions**

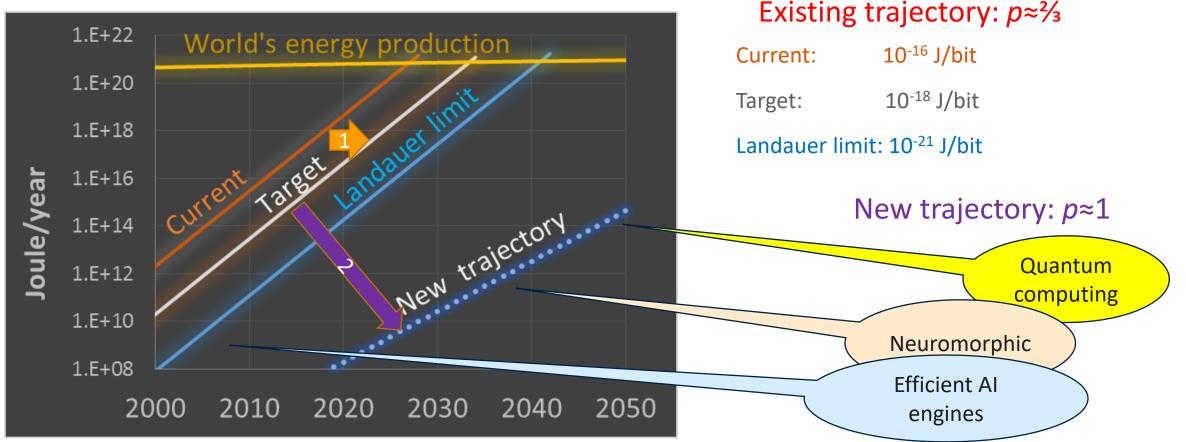

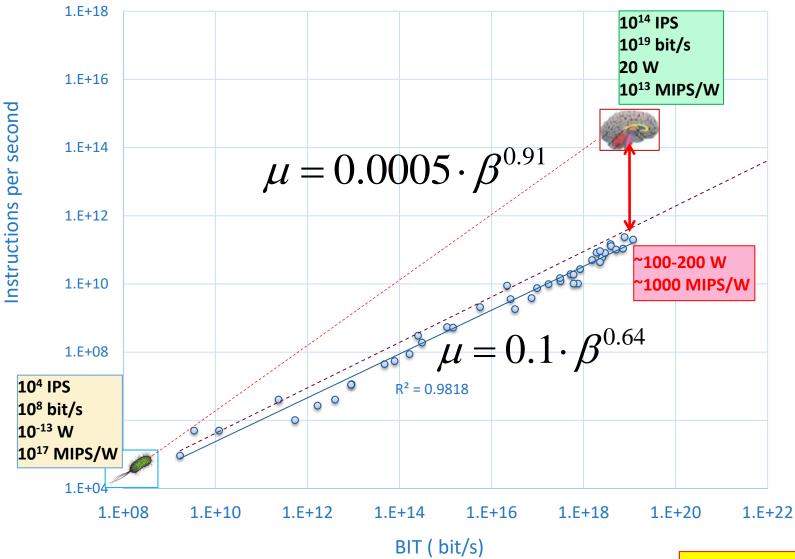

# Total energy of computing: A need to change 'computational trajectory'

(based on research by Hilbert and Lopez: M. Hilbert and P. Lopez, "The World's Technological Capacity to Store, Communicate, and Compute Information", Science 332 (2011) 60-65

$$MIPS = k (BITS)^{p}$$

Public

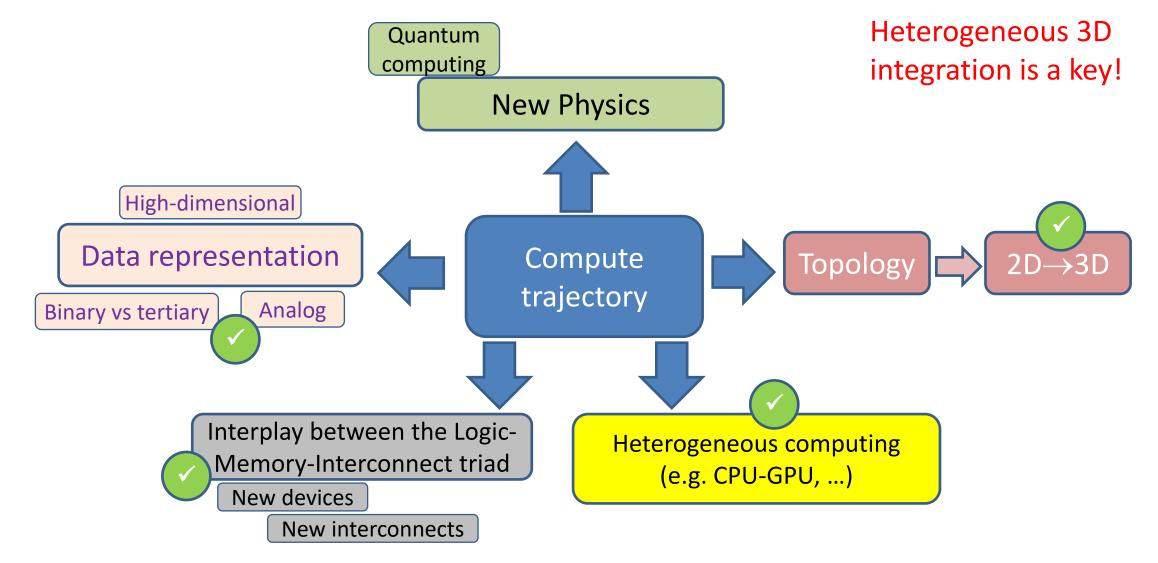

### Towards new compute trajectories for energy efficiency

# Next microelectronic revolution

We must evaluate market-driven opportunities "side-by-side" to realize lasting innovations

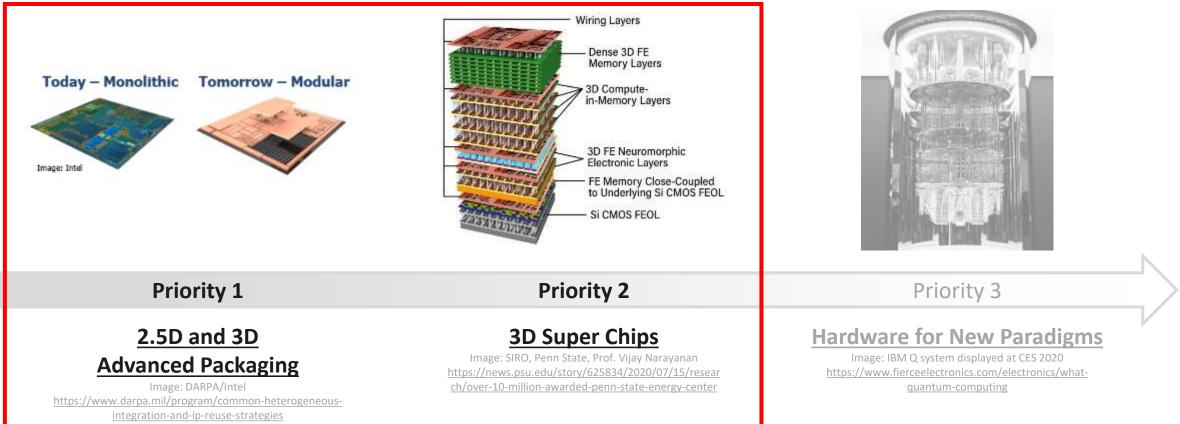

Advanced Packaging, along with 3D monolithic and 2.5D/3D heterogeneous integration, will be the key enabler of the next microelectronic revolution. In fact, advanced packaging+3D is becoming the equivalent of transistor of the Moore's Law and ITRS era.

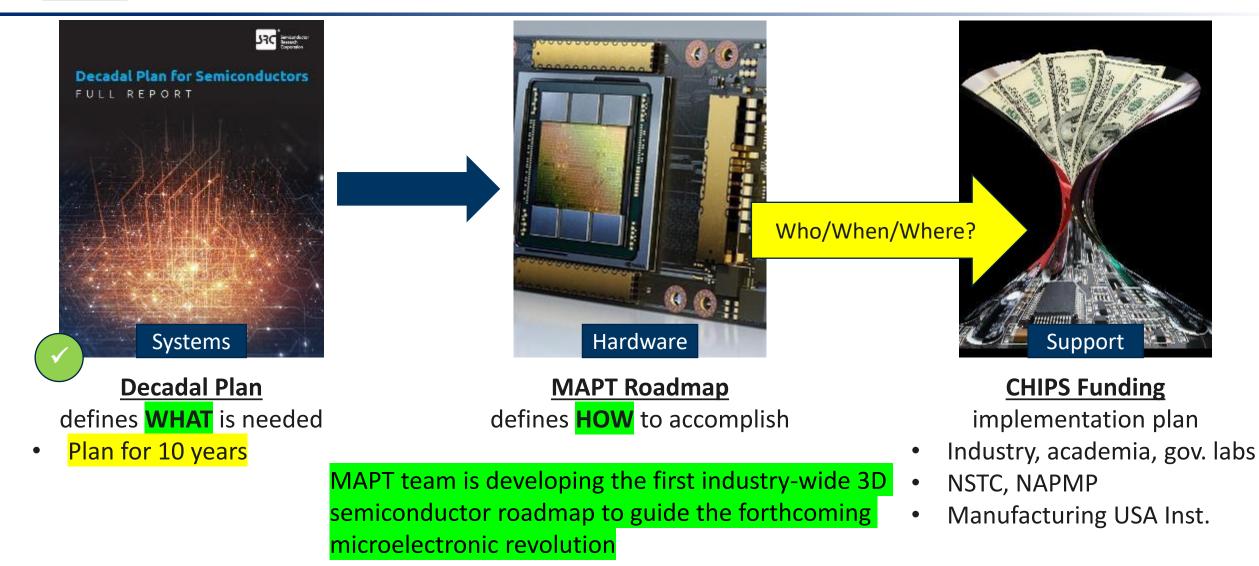

### MAPT: From Decadal Plan to actionable all-industry Roadmap

**Microelectronics and Advanced Packaging Technologies Roadmap**

# MAPT: A natural next step for Decadal Plan

MAPT

Microelectronic and Advanced Packaging Technologies Roadmap - Interim Report.

<u> Interim Report - https://srcmapt.org/about/</u>

HOME CHAPTERS ABOUT PROVIDE FEEDBACK

**106 participation organizations**

250 individual participants

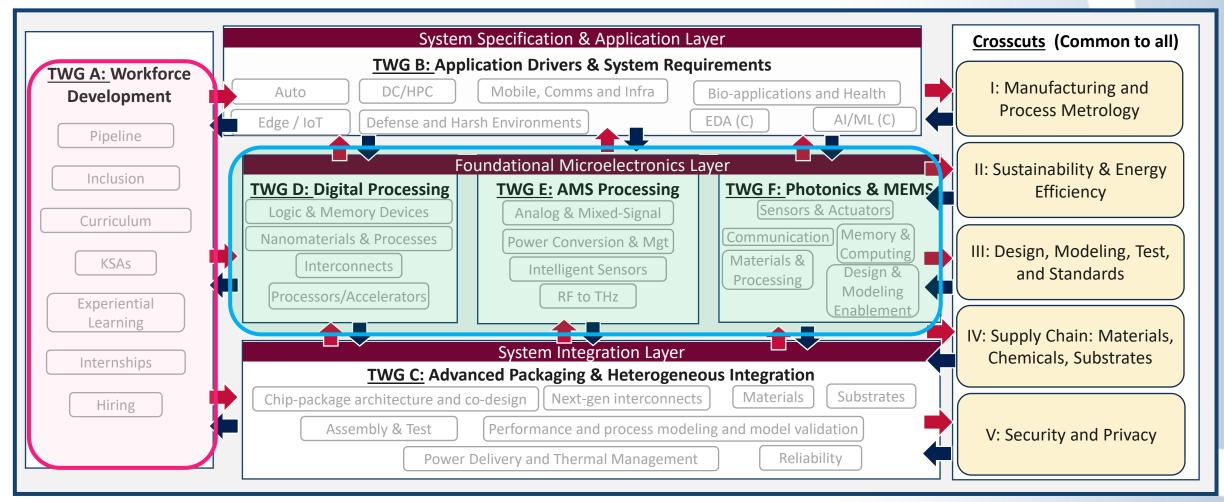

# MICROELECTRONIC AND ADVANCED PACKAGING TECHNOLOGIES ROADMAP

Final version due 31/10/2023

# **MAPT Roadmap**

**Organization Structure**

Needed: 3D-IC platform for multi-chiplet system design and advanced packaging

MAPT is the first industry-wide 3D semiconductor roadmap to guide the forthcoming microelectronic revolution - *like the ITRS has served in the past*.

# <u>ITRS</u>

### 2D transistor scaling to < 1nm

nm-scale patterning for 2D chips

**MAPT**

### Transistor scaling provides less value node-to-node

#### 3D chips: Dep+Etch is the new litho

- 1. Use ALD, ALE, or other self-limiting reactions to address 300mm equipment-related opportunities in Stacked 2D material transistors

- 2. Use ALD, ALE, or other self-limiting reactions to address 300mm equipment-related opportunities in BEOL Transistors

- 3. Use ALD, ALE, or other self-limiting reactions to address 300mm equipment-related opportunities in Thermal Management Solutions

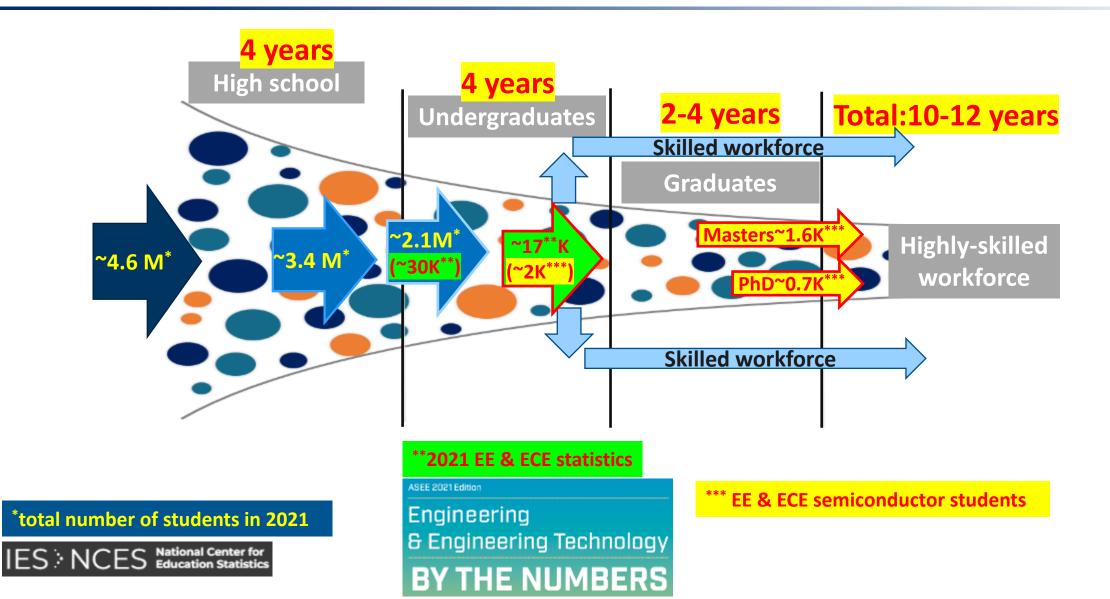

Semiconductor Workforce Development Pipeline

### Decadal Plan and MAPT highlights

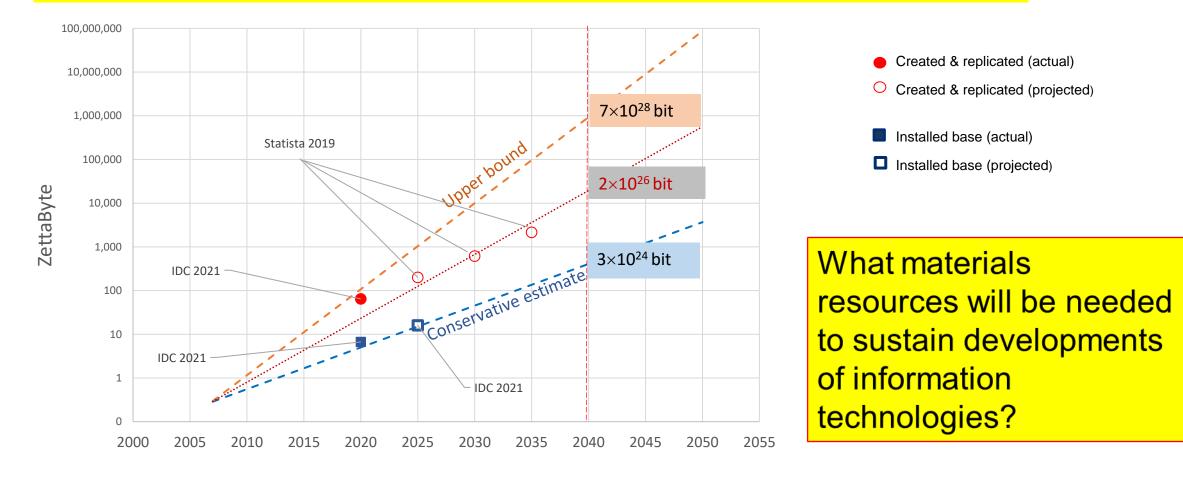

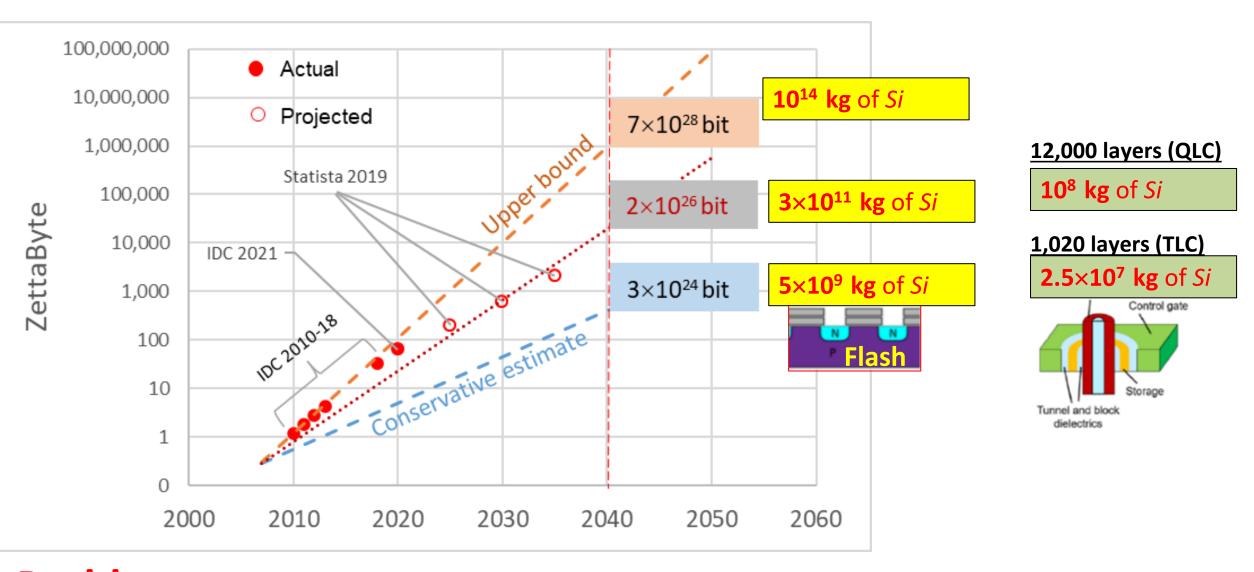

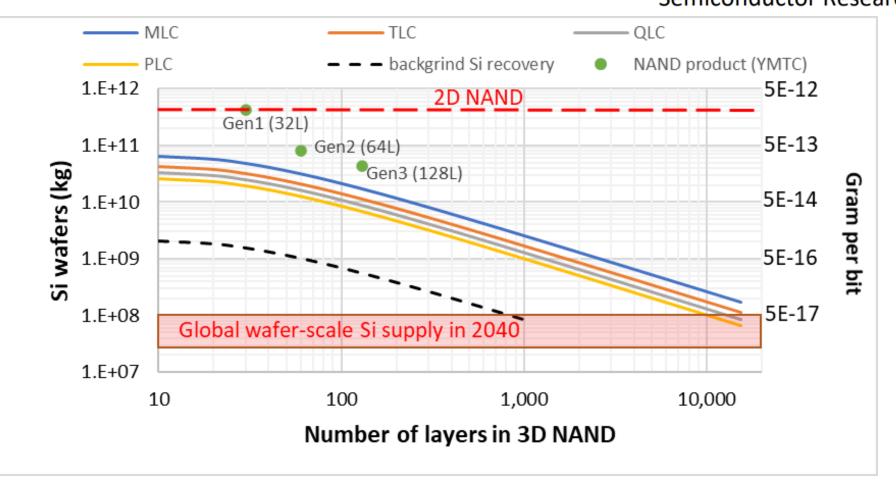

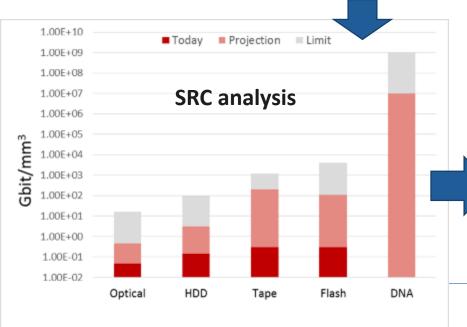

# Decadal Plan model for global data storage needs

#### Those who own the memory innovation, own the data, and own the future

# Trend: Dramatic storage needs increase

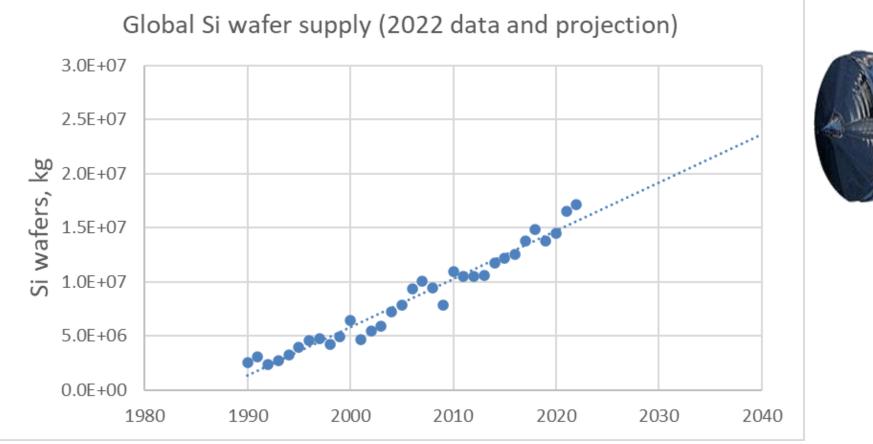

### **Problem:** *Projected annual global supply of Silicon wafers:* 2.4×10<sup>7</sup> kg in 2040

# Global Silicon Wafer Supply Trend

(updated 12/5/2022)

### IEEE VLSI Circuits & Systems Letter

QUARTERLY PUBLICATION OF IEEE COMPUTER SOCIETY TECHNICAL COMMITTEE ON VLSI (TCVLSI)

Volume 7 Issue 4 Nov 2021

#### The future of NAND flash – compute and non-volatile memory fusion!

Sean Eilert<sup>1</sup>, Steffen Hellmold<sup>2</sup>, Steve Kramer<sup>1</sup>, and Victor V. Zhirnov<sup>3</sup>

<sup>1</sup>Micron Technology Inc. <sup>2</sup>Western Digital Corp. <sup>3</sup>Semiconductor Research Corp.

### Only 3.23% of Si is used!

https://esg.tsmc.com/csr/en/update/greenManufacturing/caseStudy/44/index.html

The filter press was used to produce the recyclable high-purity silicon cake.

Waste Si from backgrind gets lost

Table S3 | Diameter and thickness of standard Si wafers

| Wafer diameter (mm) | Wafer thickness (mm) |

|---------------------|----------------------|

| 100                 | 0.525                |

| 150                 | 0.625                |

| 200                 | 0.725                |

| 300                 | 0.775                |

| 450*                | 0.925 —              |

\* Preproduction wafer diameter under development

#### TSMC Pioneers Physical Regeneration Technique for Backgrinding Wastewater

00

Recycled Industrial-grade Silicon Products Are Introduced into Steel Industry to Realize Circular Economy

2021/02/25

P.H. Chiou

Yu-Wu Chen

Fu-An Wu

n Wu

Kidd Hsu

A THE REAL PROPERTY OF THE PARTY OF THE PART

f 🍠 in 🛯

TSMC's waste management strategies primarily focus on circular economy and source reduction. A large amount of wastewater can be generated during the semiconductor advanced packaging process. In 2020, TSMC led the industry to initiate the physical regeneration technique without <u>chemical additives</u> for <u>backgrinding</u> wastewater treatment. By January 2021, TSMC has saved the use of more than 55 metric tons of chemicals. In addition, the products are transformed from inorganic sludge into high-purity industrial-grade silicon. TSMC has sold out the first batch of silicon products in December 2020, achieving a circular economy with innovation. Taking a step further, the silicon products will be used as deoxidizer in the steelmaking process.

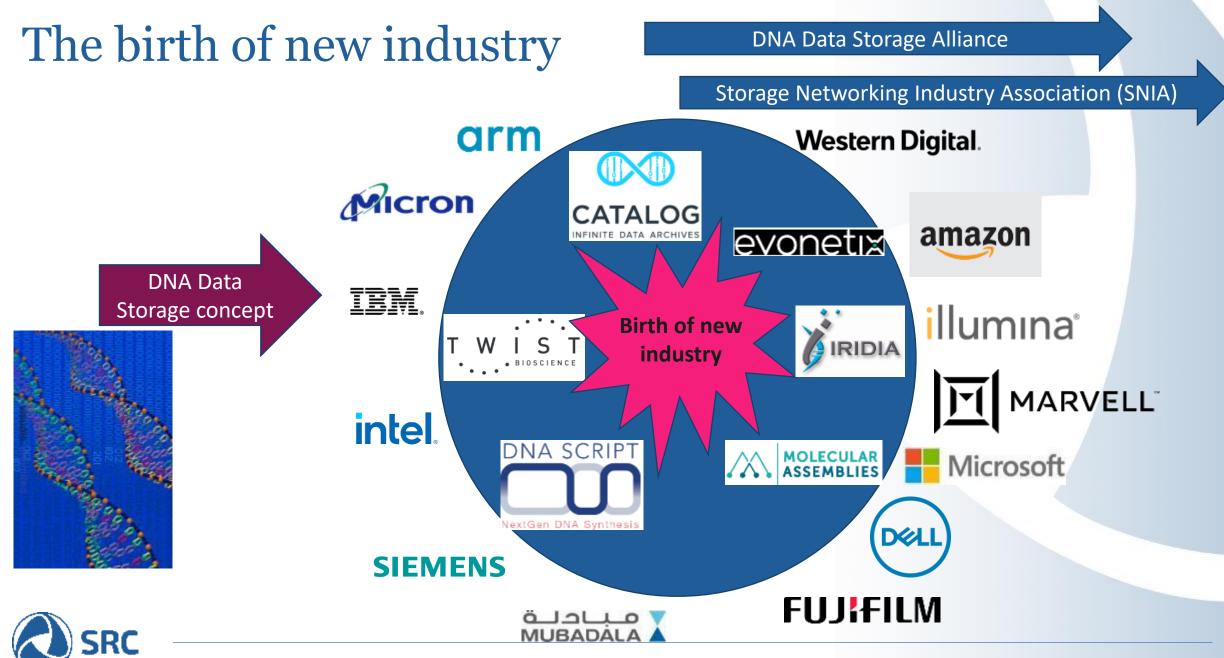

# **Creating New Industry**

Seismic Shift: Dramatic global Storage requirement increase

#### 2040 storage needs >1000 zettabytes (>10<sup>24</sup>Bytes)

#### **Grand Challenge**

Today's storage technologies <u>will not be sustainable</u> in near future due to excessive material resources needed to support the ongoing Data Explosion

Office of the Director of National Intelligence

IARPA BE THE FUTURE New Industry

IARPA's Molecular Information STorage (MIST) Program

# **Compute Energy Challenge**

### ICT ENERGY COMPUTATION AND COMMUNICATION

$MIPS = k(BITS)^{p}$

- Discover compute trajectories with  $p \sim 1$

- How do we get from  $\sim 2/3$  to 0.9 or 1?

- What "silicon" solutions can push the coefficient toward 1?

# SRC Energy consumption by three cornerstones of CPU

### **Computations vs. binary transitions**

### Estimates of computational power of human brain:

Binary information throughput:  $\beta \sim 10^{19} \text{ bit/s}$

Gitt W, "Information - the 3rd fundamental quantity", Siemens Review 56 (6): 36-41 1989 (Estimate made from the analysis of the control function of brain: language, deliberate movements, informationcontrolled functions of the organs, hormone system etc.

### $\frac{\text{Number of instruction per second}}{\mu \sim 10^8 \text{ MIPS}}$

H. Moravec, "When will computer hardware match the human brain?" J. Evolution and Technol. 1998. Vol. 1 (Estimate made from the analysis brain image processing)

Alternative trajectory may exist!

## Summary

- On March 1st, we released the Interim Report for the Microelectronic and Advanced Packaging Technologies Roadmap (MAPT)

- an industry-wide initiative of major impact on the semiconductor industry

- introduces a new comprehensive Roadmap to guide the forthcoming microelectronic revolution, like the ITRS has served in the past.

- The MAPT Roadmap manifests the transition from

- a two-dimensional (2D), smaller-transistor-centric paradigm to

- a universal 3D and heterogeneous integration microelectronics platform

- seamless integration of multiple electronic, photonic, micromechanical, etc. chiplets

- Needed: 3D-IC platform for multi-chiplet system design and advanced packaging

- Advanced packaging is new king of microelectronics!

- The MAPT Roadmap supports the 2030 Decadal Plan for Semiconductors

- projects 10-15 year targets and timelines highlighting possible solutions for the identified targets including

- Semiconductor Manufacturing Technologies

- Environmental sustainability

- Workforce Development

## **MAPT Summary**

**Total Organizations**

### <mark>106</mark>

- SRC Members

- Universities

- Government

- Other Industry

#### **TWGs by numbers**

- TWG A: Workforce Development

- TWG B: Application Drivers & System Requirements

- TWG C: Advanced Packaging & Heterogeneous Integration

- TWG D: Digital Processing

- TWG E: AMS Processing

- TWG F: Photonics & MEMS

#### University (US) - 29

Arizona State University **Binghamton University** Clarkson University Darthmouth college **Duke University** Georgia Institute of Technology Howard University Iowa State University Mass. Institute of Technology Morgan State University NC A&T State University North Carolina State University **Oregon State University** Pennsylvania State University **Purdue University** Rochester Institute of Technology Stanford University SUNY Polytechnic Institute University of California, San Diego University of California, Irvine **UCSB** UCF University of Florida U Illinois, Urbana-Champaign

University of Michigan

University of Minnesota

University of Notre Dame

University of Texas, Dallas

Washington State University

#### Industry - SRC Member - 22

ASM Advanced Micro Devices, Inc. Analog Devices, Inc. Applied Materials, Inc. Arm Boeing GlobalFoundries Inc. **IBM** Corporation **Intel Corporation** MediaTek, Inc. Micron Technology, Inc. Mubadala Technology Northrop Grumman Qualcomm NXP Semiconductors **Raytheon Technologies** Samsung Electronics Co., Ltd. Siemens EDA SK hynix Inc. Texas Instruments Incorporated Tokyo Electron Limited (TEL) TSMC University (Int'l) - 6

Indian Inst. of Tech./Kanpur KAUST Khalifa University University of Guelph

University of Sheffield

University of Toronto

Industry - Other - 33 **3D Glass Solutions** Ansys Amazon Bosch Broadcom Cadence Cardea Bio **Cirrus Logic** Cisco Systems, Inc. eFabless **Electronic Innovations** Entegris Google **Hewlett Packard Enterprise Kepler Computing** Lumoniq Memcus Microsoft MITRE Nokia Rigaku Silicon Intervention Inc. Si Ware Systems **Skywater Technologies** Softmems Synopsys, Inc.

### **MAPT Summary**

| Industry - Other – 33 (con't) |   |  |

|-------------------------------|---|--|

| Tower Semiconductor           |   |  |

| Twist Bioscience              |   |  |

| Uhnder                        |   |  |

| Western Digital Corporation   |   |  |

| X-Celeprint                   |   |  |

| Zero Asic                     |   |  |

|                               |   |  |

|                               | - |  |

Government (Agencies/National Labs) - 7 DARPA Los Alamos National Laboratory NIST Oak Ridge National Laboratory Pacific Northwest National Laboratory Sandia National Laboratories SLAC Associations/Societies - 8 America's Frontier Fund IMEC **Innovation Impact Partners** IPC Materials Research Society Razdan Research Institute SEMI Semiconductor Research Corporation

### **Total Organizations: 106**