|

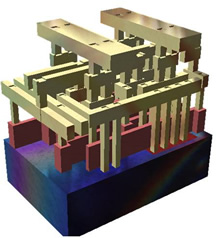

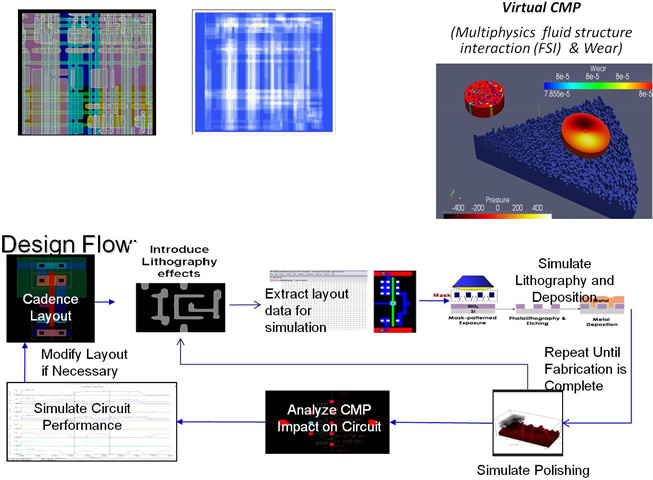

Chemical mechanical polishing (CMP) aware design for manufacturability (DFM) in integrated circuits (IC)��

| Since nanoscale integrated circuit devices are increasing in complexity and systematic variation, there is a greater need for physics-based modeling of manufacturing processes. CMP has significant influence on interconnect resistance and changes in coupling and capacitance, which can lead to large variations in timing and power. This work looks to circumvent design rules for chips sub-30nm which are low-yielding or overly conservative by introducing multi-physics CMP modeling into the computer aided design framework, without adding prohibitive computational times to the design cycle. |

|

|

Sample Results:

Select PFTL References:

Sierra Suarez J.A., Srivastava G., Higgs C.F. “A 3D Soft-EHL Model for Simulating Feature-scale Defects in Advanced Node ICs ” Proceedings of: MRS Spring Meeting. San Francisco, CA, April, 2nd 2013. |